### **Last Time Buy**

These parts are in production but have been determined to be NOT FOR NEW DESIGN or LAST TIME BUY depending on current range temperature rating and package style. Sale of this device is currently restricted to existing customer applications. The device should not be purchased for new design applications because of obsolescence in the near future. Samples are no longer available.

Date of status change: May 4, 2009

Deadline for receipt of LAST TIME BUY orders: November 4, 2009.

#### **Recommended Substitutions:**

For existing customer transition, and for new customers or new applications, refer to the <u>ACS756</u> and <u>ACS758</u>.

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

#### **Features and Benefits**

- Monolithic Hall IC for high reliability

- Single +5 V supply

- 3 kV<sub>RMS</sub> isolation voltage between terminals 4/5 and pins 1/2/3 for up to 1 minute

- 35 kHz bandwidth

- Automotive temperature range

- End-of-line factory-trimmed for gain and offset

- Ultra-low power loss: 100 μΩ internal conductor resistance

- Ratiometric output from supply voltage

- Extremely stable output offset voltage

- Small package size, with easy mounting capability

- Output proportional to AC and DC currents

#### Package: 5 pin package (leadform PFF)

#### Description

The Allegro ACS75x family of current sensor ICs provides economical and precise solutions for current sensing in industrial, automotive, commercial, and communications systems. The device package allows for easy implementation by the customer. Typical applications include motor control, load detection and management, power supplies, and overcurrent fault protection.

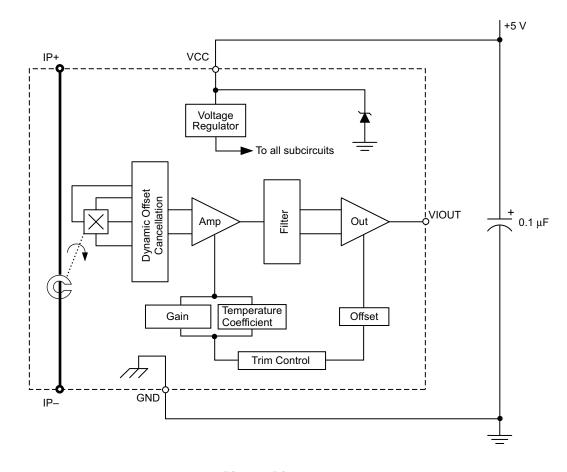

The device consists of a precision, low-offset linear Hall circuit with a copper conduction path located near the die. Applied current flowing through this copper conduction path generates a magnetic field which the Hall IC converts into a proportional voltage. Device accuracy is optimized through the close proximity of the magnetic signal to the Hall transducer. A precise, proportional voltage is provided by the low-offset, chopper-stabilized BiCMOS Hall IC, which is programmed for accuracy at the factory.

The output of the device has a positive slope (>V<sub>CC</sub>/2) when an increasing current flows through the primary copper conduction path (from terminal 4 to terminal 5), which is the path used for current sampling. The internal resistance of this conductive path is typically 100  $\mu\Omega$ , providing low power loss. The thickness of the copper conductor allows survival of the device at up to

Continued on the next page...

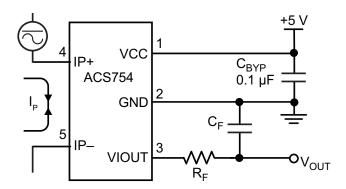

### **Typical Application**

Application 1. The ACS754 outputs an analog signal,  $V_{OUT}$ . that varies linearly with the uni- or bi-directional AC or DC primary sampled current,  $I_P$ , within the range specified.  $C_F$  is recommended for noise management, with values that depend on the application.

#### ACS754xCB-200

### Fully Integrated, Hall Effect-Based Linear Current Sensor IC with High Voltage Isolation and a Low-Resistance Current Conductor

#### **Description (continued)**

5× overcurrent conditions. The terminals of the conductive path are electrically isolated from the signal leads (pins 1 through 3). This allows the ACS75x family of sensor ICs to be used in applications requiring electrical isolation without the use of opto-isolators or other costly isolation techniques.

The device is fully calibrated prior to shipment from the factory. The ACS75x family is lead (Pb) free. All pins are coated with 100% matte tin, and there is no lead inside the package. The heavy gauge leadframe is made of oxygen-free copper.

#### Selection Guide

| Part Number                                 | T <sub>OP</sub><br>(°C) | Primary<br>Sampled<br>Current, I <sub>P</sub><br>(A) | Sensitivity<br>Sens (Typ.)<br>(mV/A) | Package   |             |                      |  |

|---------------------------------------------|-------------------------|------------------------------------------------------|--------------------------------------|-----------|-------------|----------------------|--|

|                                             |                         |                                                      |                                      | Terminals | Signal Pins | Packing <sup>1</sup> |  |

| ACS754 <del>SCB-20</del> 0-PFF <sup>2</sup> | –20 to 85               | ±200                                                 | 10                                   | Formed    | Formed      | Pulk 170 pioces/bog  |  |

| ACS754SCB-200-PSF3                          | –20 to 85               | ±200                                                 | 10                                   | Straight  | Formed      | Bulk, 170 pieces/bag |  |

<sup>&</sup>lt;sup>1</sup>Contact Allegro for additional packing options.

#### **Absolute Maximum Ratings**

| Characteristic                        | Symbol                   | Notes   | Rating                               | Units |  |

|---------------------------------------|--------------------------|---------|--------------------------------------|-------|--|

| Supply Voltage                        | V <sub>CC</sub>          |         | 16                                   | V     |  |

| Reverse Supply Voltage                | V <sub>RCC</sub>         |         | -16                                  | V     |  |

| Output Voltage                        | V <sub>IOUT</sub>        |         | 16                                   | V     |  |

| Reverse Output Voltage                | V <sub>RIOUT</sub>       |         | -0.1                                 | V     |  |

| Maximum Basic Isolation Voltage       | V <sub>ISO</sub>         |         | 353 VAC, 500 VDC, or V <sub>pk</sub> | V     |  |

| Maximum Rated Input Current           | I <sub>IN</sub>          |         | 200                                  | А     |  |

| Output Current Source                 | I <sub>OUT(Source)</sub> |         | 3                                    | mA    |  |

| Output Current Sink                   | I <sub>OUT(Sink)</sub>   |         | 10                                   | mA    |  |

| Naminal Counting Ambient Townsont     | _                        | Range K | -40 to 125                           | °C    |  |

| Nominal Operating Ambient Temperature | T <sub>A</sub>           | Range S | -20 to 85                            | °C    |  |

| Maximum Junction                      | T <sub>J</sub> (max)     |         | 165                                  | °C    |  |

| Storage Temperature                   | T <sub>stg</sub>         |         | -65 to 170                           | °C    |  |

TÜV America Certificate Number: U8V 04 11 54214 001

Fire and Electric Shock EN60950-1:2001

<sup>&</sup>lt;sup>2</sup>Variant is in production but has been determined to be NOT FOR NEW DESIGN. This classification indicates that sale of the variant is currently restricted to existing customer applications. The variant should not be purchased for new design applications because obsolescence in the near future is probable. Samples are no longer available. Status change: May 4, 2009.

<sup>3</sup> Variant is in production but has been determined to be LAST TIME BUY. This classification indicates that the variant is obsolete and notice has been given. Sale of the variant is currently restricted to existing customer applications. The variant should not be purchased for new design applications because of obsolescence in the near future. Samples are no longer available. Status date change May 4, 2009. Deadline for receipt of LAST TIME BUY orders is November 4, 2009.

#### **Functional Block Diagram**

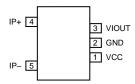

#### **Pin-out Diagram**

#### **Terminal List Table**

| Number | Name  | Description                        |  |

|--------|-------|------------------------------------|--|

| 1      | VCC   | Device power supply pin            |  |

| 2      | GND   | Signal ground pin                  |  |

| 3      | VIOUT | Analog output signal pin           |  |

| 4      | IP+   | Terminal for current being sampled |  |

| 5      | IP-   | Terminal for current being sampled |  |

#### ACS754xCB-200

# Fully Integrated, Hall Effect-Based Linear Current Sensor IC with High Voltage Isolation and a Low-Resistance Current Conductor

#### ELECTRICAL CHARACTERISTICS, over operating ambient temperature range unless otherwise stated

| Characteristic                | Symbol                | Test Conditions                                            | Min.    | Тур.               | Max.  | Units |

|-------------------------------|-----------------------|------------------------------------------------------------|---------|--------------------|-------|-------|

| Primary Sampled Current       | Ι <sub>Ρ</sub>        |                                                            | -200    | -                  | 200   | А     |

| Supply Voltage                | V <sub>CC</sub>       |                                                            | 4.5     | 5.0                | 5.5   | V     |

| Supply Current                | I <sub>CC</sub>       | V <sub>CC</sub> = 5.0 V, output open                       | 6.5     | 8                  | 10    | mA    |

| Output Resistance             | R <sub>OUT</sub>      | I <sub>OUT</sub> = 1.2 mA                                  | _       | 1                  | 2     | Ω     |

| Output Capacitance Load       | C <sub>LOAD</sub>     | VOUT to GND                                                | _       | _                  | 10    | nF    |

| Output Resistive Load         | R <sub>LOAD</sub>     | VOUT to GND                                                | 4.7     | _                  | _     | kΩ    |

| Primary Conductor Resistance  | R <sub>PRIMARY</sub>  | I <sub>P</sub> = ±50A; T <sub>A</sub> = 25°C               | _       | 100                | _     | μΩ    |

| Isolation Voltage             | V <sub>ISO</sub>      | Pins 1-3 and 4-5; 60 Hz, 1 minute                          | 3.0     | _                  | _     | kV    |

| PERFORMANCE CHARACTERIS       | STICS, -20°C to       | +85°C, V <sub>CC</sub> = 5 V unless otherwise spe          | ecified |                    |       |       |

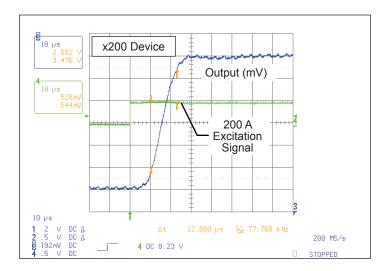

| Propagation time              | t <sub>PROP</sub>     | I <sub>P</sub> = ±100 A, T <sub>A</sub> = 25°C             | _       | 4                  | _     | μs    |

| Response time                 | t <sub>RESPONSE</sub> | I <sub>P</sub> = ±100 A, T <sub>A</sub> = 25°C             | _       | 11                 | _     | μs    |

| Rise time                     | t <sub>r</sub>        | I <sub>P</sub> = ±100 A, T <sub>A</sub> = 25°C             | _       | 10                 | _     | μs    |

| Frequency Bandwidth           | f                     | −3 dB, T = 25°C                                            | _       | 35                 | _     | kHz   |

| 0                             | Sens                  | Over full range of I <sub>P</sub> , T <sub>A</sub> = 25°C  | _       | 10.0               | _     | mV/A  |

| Sensitivity                   |                       | Over full range of I <sub>P</sub>                          | 9.5     | _                  | 10.5  | mV/A  |

| Noise                         | V <sub>NOISE</sub>    | Peak-to-peak, T <sub>A</sub> = 25°C,<br>no external filter | _       | 35                 | _     | mV    |

| Linearity                     | E <sub>LIN</sub>      | Over full range of I <sub>P</sub>                          | _       | _                  | ±1.2  | %     |

| Symmetry                      | E <sub>SYM</sub>      | Over full range of I <sub>P</sub>                          | 98      | 100                | 102   | %     |

| Zero Current Output Voltage   | $V_{OUT(Q)}$          | I = 0 A, T <sub>A</sub> = 25°C                             | _       | V <sub>CC</sub> /2 | _     | V     |

| Electrical Offset Voltage     |                       | I = 0 A, T <sub>A</sub> = 25°C                             | -10     | _                  | 10    | mV    |

| (Magnetic error not included) | V <sub>OE</sub>       | I = 0 A                                                    | -20     | _                  | 20    | mV    |

| Magnetic Offset Error         | I <sub>ERROM</sub>    | I = 0 A, after excursion of 200 A                          | _       | ±0.15              | ±0.50 | Α     |

| Total Output Error            | E                     | Over full range of I <sub>P</sub> , T <sub>A</sub> = 25°C  | _       | ±1.0               | -     | %     |

| (Including all offsets)       | E <sub>TOT</sub>      | Over full range of I <sub>P</sub>                          | _       | _                  | ±5.0  | %     |

#### **Definitions of Accuracy Characteristics**

**Sensitivity (Sens).** The change in device output in response to a 1 A change through the primary conductor. The sensitivity is the product of the magnetic circuit sensitivity (G/A) and the linear IC amplifier gain (mV/G). The linear IC amplifier gain is programmed at the factory to optimize the sensitivity (mV/A) for the full-scale current of the device.

**Noise (V**<sub>NOISE</sub>). The product of the linear IC amplifier gain (mV/G) and the noise floor for the Allegro Hall effect linear IC ( $\approx 1$  G). The noise floor is derived from the thermal and shot noise observed in Hall elements. Dividing the noise (mV) by the sensitivity (mV/A) provides the smallest current that the device is able to resolve.

**Linearity** ( $E_{LIN}$ ). The degree to which the voltage output from the IC varies in direct proportion to the primary current through its full-scale amplitude. Nonlinearity in the output can be attributed to the saturation of the flux concentrator approaching the full-scale current. The following equation is used to derive the linearity:

$$100 \left\{ 1 - \left[ \frac{\Delta \text{ gain} \times \% \text{ sat ( } V_{\text{IOUT\_full-scale amperes } - V_{\text{IOUT(Q)}})}}{2 \left( V_{\text{IOUT\_half-scale amperes } - V_{\text{IOUT(Q)}} \right)} \right] \right\}$$

where

$\Delta$  gain = the gain variation as a function of temperature changes from 25°C,

% sat = the percentage of saturation of the flux concentrator, which becomes significant as the current being sampled approaches full-scale  $\pm I_P$ , and

$V_{IOUT\_full\text{-scale amperes}} = \text{the output voltage (V) when the sampled current approximates full-scale } \pm I_P \,.$

**Symmetry** ( $E_{SYM}$ ). The degree to which the absolute voltage output from the IC varies in proportion to either a positive or negative full-scale primary current. The following equation is used to derive symmetry:

$$100 \left( \frac{V_{\text{IOUT}} + \text{full-scale amperes} - V_{\text{IOUT}(Q)}}{V_{\text{IOUT}(Q)} - V_{\text{IOUT}} - \text{full-scale amperes}} \right)$$

**Quiescent output voltage (V**<sub>IOUT(Q)</sub>). The output of the device when the primary current is zero. For a unipolar supply voltage, it nominally remains at  $V_{CC}/2$ . Thus,  $V_{CC} = 5$  V translates into  $V_{IOUT(Q)} = 2.5$  V. Variation in  $V_{OUT(Q)}$  can be attributed to the resolution of the Allegro linear IC quiescent voltage trim, magnetic hysteresis, and thermal drift.

Electrical offset voltage ( $V_{OE}$ ). The deviation of the device output from its ideal quiescent value of  $V_{CC}/2$  due to nonmagnetic causes.

**Magnetic offset error (I**<sub>ERROM</sub>). The magnetic offset is due to the residual magnetism (remnant field) of the core material. The magnetic offset error is highest when the magnetic circuit has been saturated, usually when the device has been subjected to a full-scale or high-current overload condition. The magnetic offset is largely dependent on the material used as a flux concentrator. The larger magnetic offsets are observed at the lower operating temperatures.

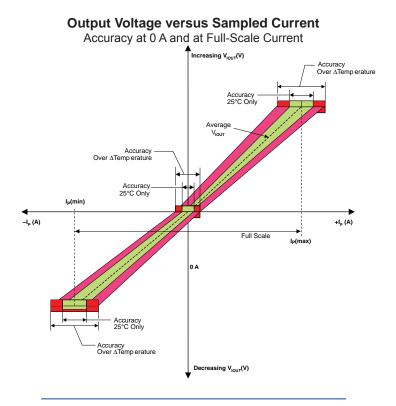

**Accuracy** ( $E_{TOT}$ ). The accuracy represents the maximum deviation of the actual output from its ideal value. This is also known as the total output error. The accuracy is illustrated graphically in the output voltage versus current chart on the following page.

Accuracy is divided into four areas:

- **0** A at 25°C. Accuracy at the zero current flow at 25°C, without the effects of temperature.

- 0 A over Δ temperature. Accuracy at the zero current flow including temperature effects.

- Full-scale current at 25°C. Accuracy at the full-scale current at 25°C, without the effects of temperature.

- Full-scale current over Δ temperature. Accuracy at the full-scale current flow including temperature effects.

5

### **Definitions of Dynamic Response Characteristics**

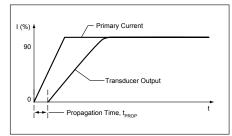

**Propagation delay (t<sub>PROP</sub>).** The time required for the device output to reflect a change in the primary current signal. Propagation delay is attributed to inductive loading within the linear IC package, as well as in the inductive loop formed by the primary conductor geometry. Propagation delay can be considered as a fixed time offset and may be compensated.

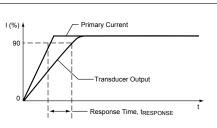

Response time ( $t_{RESPONSE}$ ). The time interval between a) when the primary current signal reaches 90% of its final value, and b) when the device reaches 90% of its output corresponding to the applied current.

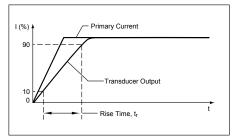

**Rise time** ( $t_r$ ). The time interval between a) when the device reaches 10% of its full scale value, and b) when it reaches 90% of its full scale value. The rise time to a step response is used to derive the bandwidth of the device, in which  $f(-3 \text{ dB}) = 0.35/t_r$ . Both  $t_r$  and  $t_{RESPONSE}$  are detrimentally affected by eddy current losses observed in the conductive IC ground plane.

6

#### **Step Response** No external filter, T<sub>A</sub>=25°C

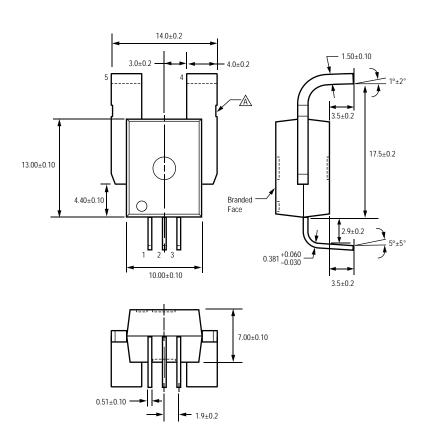

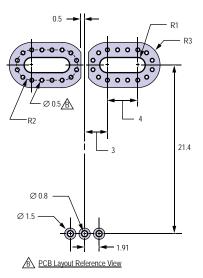

#### Package CB, 5-pin package Leadform PFF

Creepage distance, current terminals to signal pins: 7.25 mm Clearance distance, current terminals to signal pins: 7.25 mm Package mass: 4.63 g typical

NNNNNNN

TTT-AAA

LILLLLLL

YYWW A

1 | | | |

#### A Standard Branding Reference View

- N = Device part number

- T = Temperature code

- A = Amperage range L = Lot number

- Y = Last two digits of year of manufacture

- W = Week of manufacture

- $\mathcal{A}$  = Supplier emblem

For Reference Only; not for tooling use (reference DWG-9111, DWG-9110) Dimensions in millimeters

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

A Dambar removal intrusion

Perimeter through-holes recommended

Branding scale and appearance at supplier discretion

Copyright ©2004-2009, Allegro MicroSystems, Inc.

The products described herein are manufactured under one or more of the following U.S. patents: 5,619,137; 5,621,319; 6,781,359; 7,075,287; 7,166,807; 7,265,531; 7,425,821; or other patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com